#### DEPARTMENT OF COMPUTER SYSTEM ENGINEERING

#### Digital Integrated Circuits - ENCS333

2<sup>nd</sup> SEMESTER (2015-2016)

#### Dr. Khader Mohammad Lecture #6 Introduction Layout of an Inverter and basic gates

## **Digital Integrated Circuits**

|    | Course topics and Schedule                           |  |  |  |  |  |  |  |  |  |  |

|----|------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

|    | Subject                                              |  |  |  |  |  |  |  |  |  |  |

| 1  | Introduction to Digital Integrated Circuits Design   |  |  |  |  |  |  |  |  |  |  |

| 2  | Semiconductor material: pn-junction, NMOS, PMOS      |  |  |  |  |  |  |  |  |  |  |

| 3  | IC Manufacturing and Design Metrics CMOS             |  |  |  |  |  |  |  |  |  |  |

| 4  | Transistor Devices and Logic Design                  |  |  |  |  |  |  |  |  |  |  |

|    | The CMOS inverter                                    |  |  |  |  |  |  |  |  |  |  |

| 5  | Combinational logic structures                       |  |  |  |  |  |  |  |  |  |  |

| 7  | Sequential logic gates; Latches and Flip-Flops       |  |  |  |  |  |  |  |  |  |  |

| 6  | Layout of an Inverter and basic gates                |  |  |  |  |  |  |  |  |  |  |

| 8  | Parasitic Capacitance Estimation                     |  |  |  |  |  |  |  |  |  |  |

| 9  | Device modeling parameterization from I-V curves.    |  |  |  |  |  |  |  |  |  |  |

|    | Short Test                                           |  |  |  |  |  |  |  |  |  |  |

| 10 | Arithmetic building blocks                           |  |  |  |  |  |  |  |  |  |  |

| 11 | Interconnect: R, L and C - Wire modeling             |  |  |  |  |  |  |  |  |  |  |

| 12 | Timing                                               |  |  |  |  |  |  |  |  |  |  |

|    | Power dissipation;                                   |  |  |  |  |  |  |  |  |  |  |

| 13 | SPICE Simulation Techniques ( Project )              |  |  |  |  |  |  |  |  |  |  |

| 14 | Memories and array structures                        |  |  |  |  |  |  |  |  |  |  |

|    | Midterm                                              |  |  |  |  |  |  |  |  |  |  |

| 15 | Clock Distribution                                   |  |  |  |  |  |  |  |  |  |  |

| 16 | Supply and Threshold Voltage Scaling                 |  |  |  |  |  |  |  |  |  |  |

| 17 | Reliability and IC qualification process             |  |  |  |  |  |  |  |  |  |  |

| 18 | Advanced Voltage Scaling Techniques                  |  |  |  |  |  |  |  |  |  |  |

| 19 | Power Reduction Through Switching Activity Reduction |  |  |  |  |  |  |  |  |  |  |

| 20 | CAD tools and algorithms                             |  |  |  |  |  |  |  |  |  |  |

| 24 | Final & Project discussion                           |  |  |  |  |  |  |  |  |  |  |

#### DIGITAL GATES Fundamental Parameters

- Functionality

- Reliability, Robustness

- Area

- Performance

- Speed (delay)

- Power Consumption

- Energy

### Layout

#### Layout

#### **Real silicon**

| Process (µ)    |                                    | 0.25  | 0.18  | 0.13  | 0.10  | 0.07  | 0.05  |

|----------------|------------------------------------|-------|-------|-------|-------|-------|-------|

| $V_{DD}$ (V)   |                                    | 2     | 1.8   | 1.5   | 1.2   | 0.9   | 0.7   |

| $L_{eff}$ (nm) |                                    | 160   | 100   | 70    | 50    | 35    | 25    |

| $t_{ox}$ (A)   |                                    | 50    | 45    | 30    | 25    | 20    | 15    |

| Levels         |                                    | 6     | 6     | 7     | 8     |       | 9     |

|                | Н (µ)                              | 0.2   | 0.15  | 0.13  | 0.1   | 0.07  | 0.07  |

| Poly           | W (µ)                              | 0.25  | 0.18  | 0.13  | 0.1   | 0.07  | 0.05  |

|                | space (µ)                          | 0.25  | 0.18  | 0.13  | 0.1   | 0.07  | 0.05  |

|                | sheet $\mathbf{p} (\Omega / \Box)$ | 4     | 5.3   | 6.2   | 8     | 11.4  | 11.4  |

|                | Η (μ)                              | 0.5   | 0.46  | 0.34  | 0.26  | 0.2   | 0.14  |

|                | W (µ)                              | 0.30  | 0.23  | 0.17  | 0.13  | 0.1   | 0.07  |

| $M_{1-2}$      | space (µ)                          | 0.30  | 0.23  | 0.17  | 0.13  | 0.1   | 0.07  |

|                | sheet $\rho$ ( $\Omega/\Box$ )     | 0.044 | 0.048 | 0.065 | 0.085 | 0.11  | 0.16  |

|                | t <sub>ins</sub> (nm)              | 650   | 500   | 360   | 320   | 270   | 210   |

| M3-4           | Η (μ)                              | 0.9   | 0.8   | 0.7   | 0.55  | 0.4   | 0.28  |

|                | W (µ)                              | 0.6   | 0.5   | 0.4   | 0.3   | 0.2   | 0.14  |

|                | space (µ)                          | 0.6   | 0.5   | 0.4   | 0.3   | 0.2   | 0.14  |

|                | sheet $\rho$ ( $\Omega/\Box$ )     | 0.024 | 0.028 | 0.031 | 0.04  | 0.055 | 0.079 |

|                | t <sub>ins</sub> (nm)              | 900   | 800   | 700   | 600   | 500   | 400   |

|                | H (µ)                              | 2.5   | 2.5   | 1.5   | 1.2   | 1.0   | 0.8   |

|                | W (µ)                              | 2.0   | 2.0   | 1.0   | 1.0   | 0.6   | 0.5   |

| M5-6           | space (µ)                          | 2.0   | 2.0   | 1.0   | 1.0   | 0.6   | 0.5   |

|                | sheet $\rho$ ( $\Omega/\Box$ )     | 0.009 | 0.009 | 0.015 | 0.018 | 0.022 | 0.028 |

|                | t <sub>ins</sub> (nm)              | 1400  | 1400  | 900   | 800   | 700   | 600   |

|                | H (µ)                              |       |       | 2.5   | 2.5   | 1.5   | 1.4   |

|                | W (µ)                              |       |       | 2.0   | 2.0   | 1.0   | 0.9   |

| M7-8           | space (µ)                          |       |       | 2.0   | 2.0   | 1.0   | 0.9   |

|                | sheet $\rho$ ( $\Omega/\Box$ )     |       |       | 0.009 | 0.009 | 0.015 | 0.016 |

|                | t <sub>ins</sub> (nm)              |       | —     | 1400  | 1400  | 900   | 800   |

|                | Н (µ)                              | —     |       | -     |       | 2.5   | 2.5   |

|                | W (µ)                              | —     | —     | —     |       | 2.0   | 2.0   |

| M9             | space (µ)                          | —     |       |       |       | 2.0   | 2.0   |

|                | sheet $\rho$ ( $\Omega/\Box$ )     |       |       |       |       | 0.009 | 0.009 |

|                | t <sub>ins</sub> (nm)              | —     | —     |       | —     | 1400  | 1400  |

| Via            | size (µ)                           | 0.55  | 0.26  | 0.2   | 0.16  | 0.12  | 0.09  |

| (M1-M2)        | $R(\Omega)$                        | 0.95  | 1.32  | 1.61  | 2.23  | 3.35  | 4.63  |

|                | κ                                  | 3.3   | 2.7   | 2.3   | 2     | 1.8   | 1.5   |

## **Design Rules**

- Design rules are an abstraction of the fabrication process that specify various geometric constraints on how different masks can be drawn.

- Design rules can be absolute measurements (e.g. in nm) or scaled to an abstract unit, the lambda. Lambda-based designs are scaled to the appropriate absolute units depending on the manufacturing process finally used.

## **Design Rules**

- Interface between designer and process engineer

- Guidelines for constructing process masks

- Unit dimension: Minimum line width

- scalable design rules: lambda parameter

- absolute dimensions (micron rules)

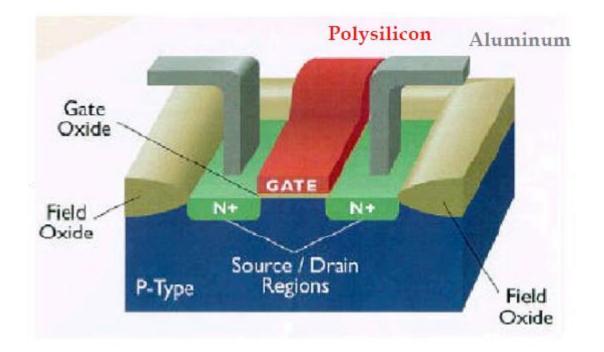

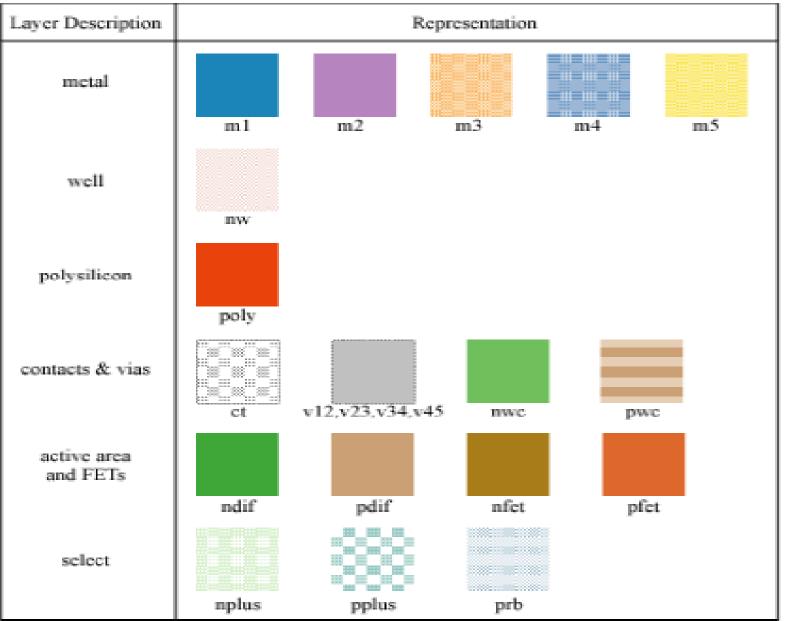

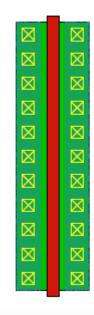

## **CMOS Process Layers**

| Layer                | Color   | Representation |

|----------------------|---------|----------------|

| Well (p,n)           | Yellow  |                |

| Active Area (n+,p+)  | Green   |                |

| Select (p+,n+)       | Green   | C              |

| Polysilicon          | Red     |                |

| Metal1               | Blue    |                |

| Metal2               | Magenta |                |

| Contact To Poly      | Black   |                |

| Contact To Diffusion | Black   |                |

| Via                  | Black   |                |

|                      |         |                |

#### Layers in 0.25 µm CMOS process

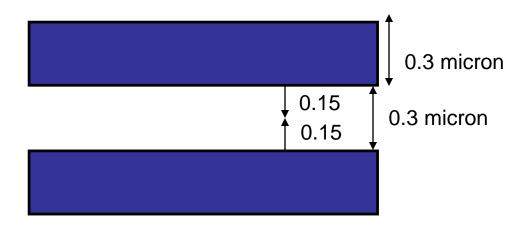

## Intra-Layer Design Rules

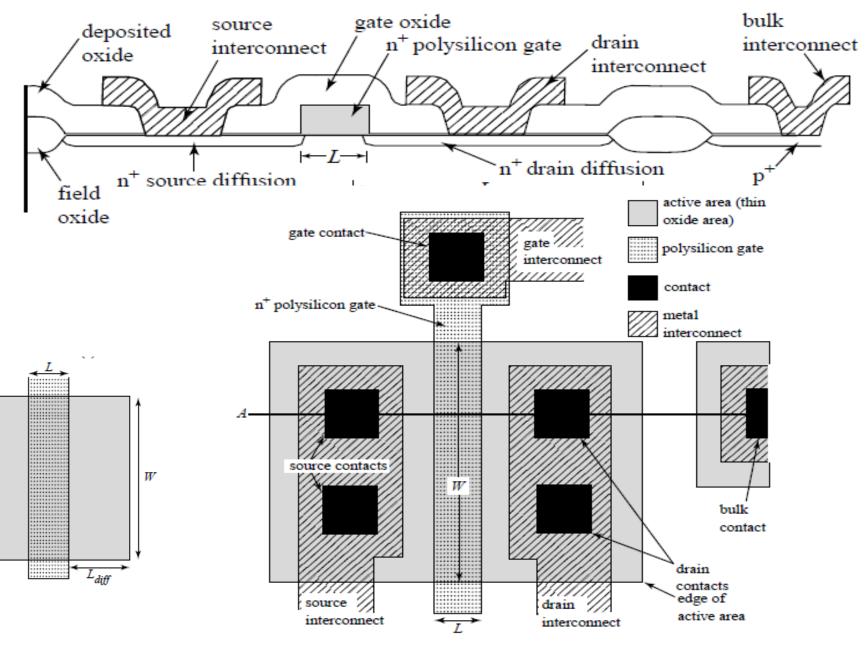

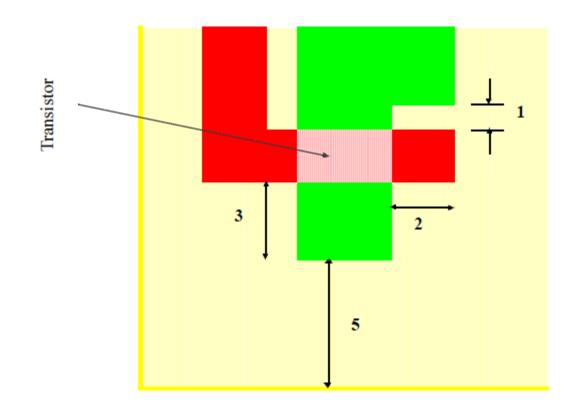

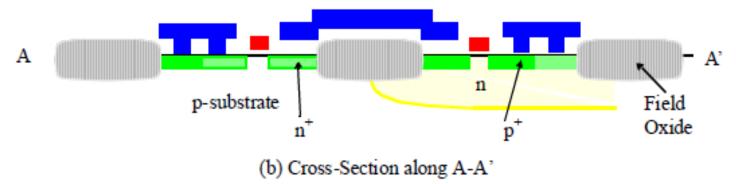

#### **Transistor Layout**

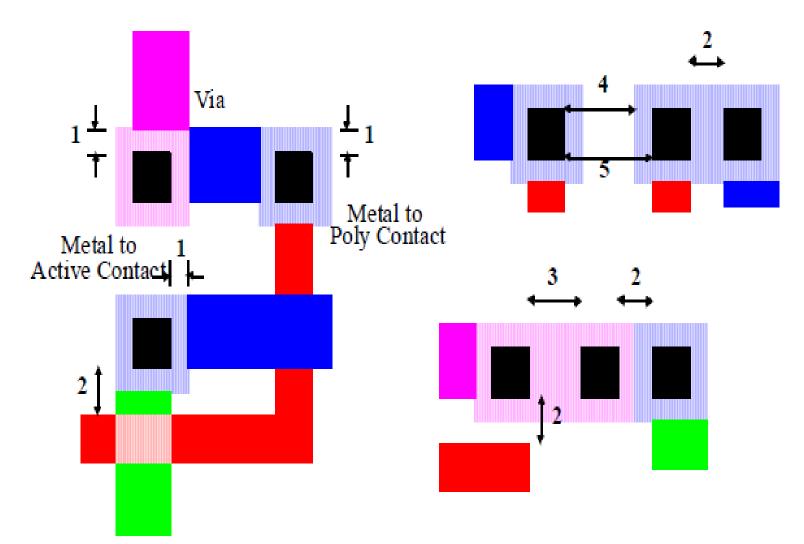

#### Vias and Contacts

#### Select Layer

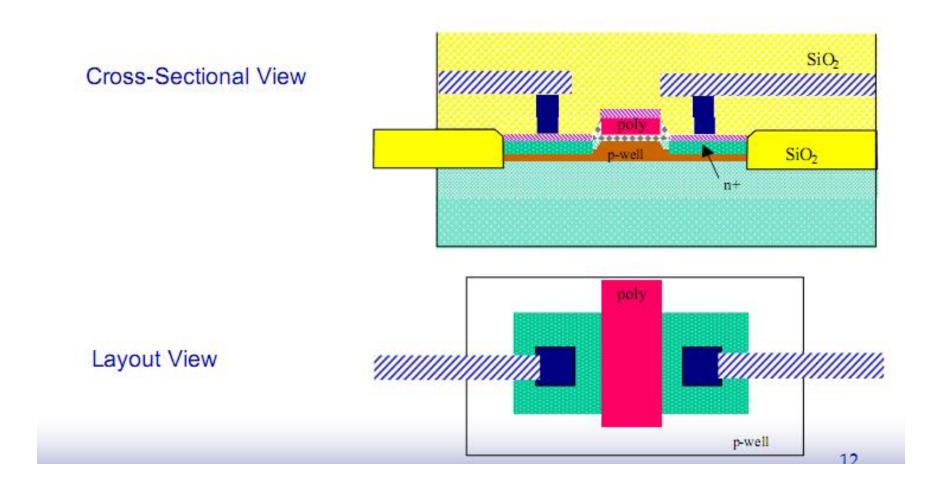

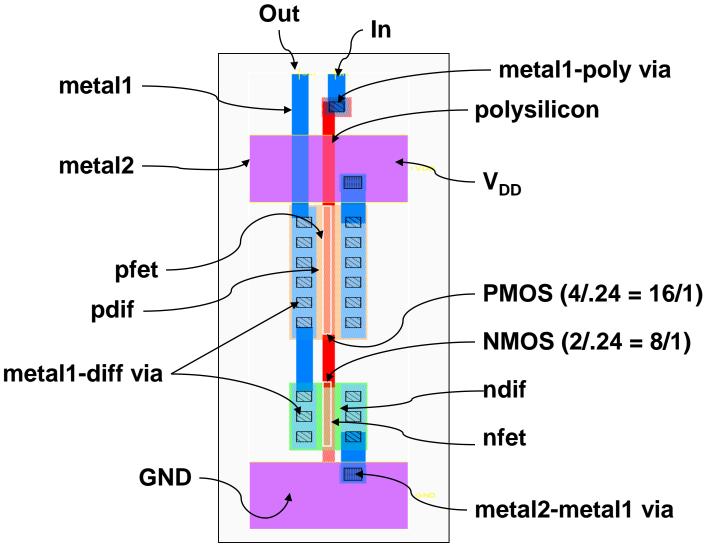

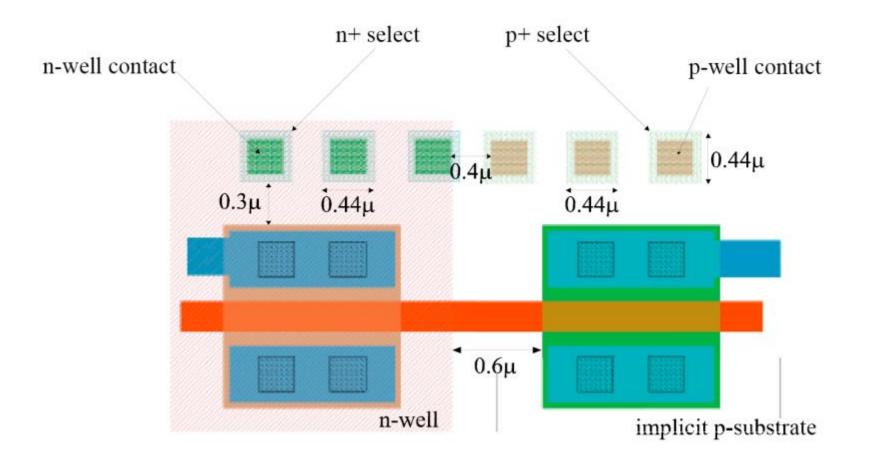

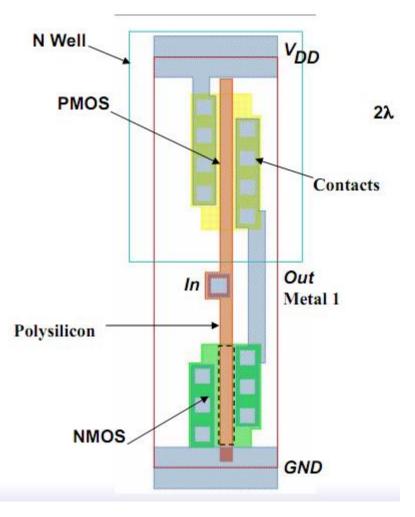

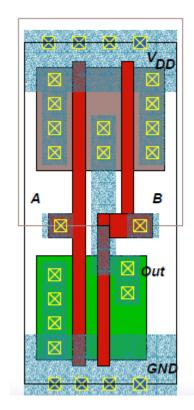

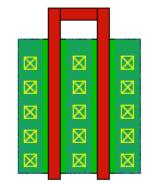

## **CMOS** Inverter Layout

## Lambda-based Design Rules

- One lambda ( $\lambda$ )= one half of the "minimum" mask dimension.

- Typically the length of a transistor channel is  $2\lambda$ .

- Usually all edges must be "on grid", e.g., in the MOSIS scalable rules, all edges must be on a lambda grid.

#### Layout Editor

| ile Edit     | View  | Mask | Tool | Misc  | Local       | Help | mai                      | n mode | . BU | T-1              | sele      | icts,  | BUT-   | 2 mo   | ves s | electi | on, f | B  |

|--------------|-------|------|------|-------|-------------|------|--------------------------|--------|------|------------------|-----------|--------|--------|--------|-------|--------|-------|----|

| uto          |       |      |      |       |             |      |                          |        |      |                  |           |        |        |        |       |        |       | 1  |

| cells-       |       |      |      |       |             |      | 1212                     |        |      | 181              | 22        |        |        |        |       |        |       |    |

| - 201-       |       | _    | -    | -     | -           | - 10 | CALCULA.                 |        | - 11 |                  | 200       | -      | -      | -      |       |        | _     | 12 |

| metal        |       |      |      |       |             |      | 18 H                     |        |      |                  |           |        |        |        |       |        |       |    |

| m5           |       |      | 100  |       | 16.000      | 120  | 0.08                     |        |      | 200              |           | 220    | 1000   | 1000   |       | 1000   |       | 1  |

| 945          |       | _    |      |       |             | 1    | 1000                     | fet    |      | 14               | 2         | 1000   | 1000   | and a  | _     |        |       |    |

|              |       |      |      | 244   | 123         | 1.23 | 23                       | 1000   |      |                  |           | E      | 144    | 3      |       |        |       |    |

| 934          |       | _    | -    | - 223 | 1           | 32.  | 1000                     |        |      | 100              | 10        |        | 222    | 8      | -     |        |       | ł. |

| v23          |       |      |      | C     |             |      |                          |        |      |                  |           | E      | 1      | 1      |       |        |       |    |

| m2           |       |      |      | 1 (C) |             |      | 16111                    |        |      | 13               | 200       | 222    | 1000   | 1010   |       |        |       | F  |

| ¥12          |       | _    | -    | -     |             | - 24 | Contraction of the       |        |      |                  | 22        |        | -      | -      | -     |        |       |    |

| m1           |       |      |      | Est   | 153         | 12   | Conversion in            | Sec. 1 |      | 24               |           | E      | 1923   | 3      |       |        |       |    |

| 8 d.         |       |      |      | 1000  | -33         |      | 1.0                      |        |      |                  | 511       |        | 1333   | 1      |       |        |       | 15 |

| active       |       |      | _    | 033   | 42.3        | 10   | Hereit                   |        | _    | 101              | 2121      |        |        | 2      |       |        |       |    |

| poly         |       |      |      |       | 1005        | 7/1  | Contraction in which the |        |      | 15.              |           | 101200 | CONT S | 1000   |       |        |       | П  |

| nfet         |       |      |      | -     | -           |      |                          |        |      | 1 10 1<br>1 10 1 | Sec. Sec. | -      |        | 1      |       |        |       | 13 |

| pfet         |       |      |      |       | 11          | 8    |                          |        |      | 100              |           | 1000   | 1      | 8      |       |        |       |    |

| ndif<br>pdif |       |      |      | 1 and | 100         | 1.00 | 1.12                     | X 2.0  | 0.24 |                  |           | 100    | 1993   | 1      |       |        |       |    |

| awe          |       | _    | _    | -     |             |      | 100.00                   |        |      | 100              | 212       | -      |        | 1      |       |        |       |    |

| pwc          |       |      |      | 10    | CONTRACT OF | . 81 | 1911                     |        |      |                  |           | 112111 | 11000  | CELE . |       |        |       |    |

| other        |       |      |      | -     |             | 100  | 1.000                    |        |      |                  | 35        |        |        | -      |       |        |       | f. |

| INF INF      |       |      |      |       |             | 1    | Sec.                     |        |      | 100              | 500       |        |        |        |       |        |       |    |

| pplus        |       |      | 1000 |       |             | . 20 | 1000                     | 1      |      | 8-9- A           | 518       |        |        | 1 2    |       |        |       | 18 |

| nplus        |       |      | -    | -     | -           | _    |                          |        |      |                  | _         |        | -      | -      | -     |        |       |    |

| 😒 prb        |       |      |      |       |             |      |                          |        |      |                  |           |        |        |        |       |        |       |    |

|              |       |      |      |       |             |      |                          |        |      |                  |           |        |        |        |       |        |       |    |

|              |       |      | -    | -     |             |      | _                        |        | _    | _                |           |        |        | -      |       |        |       | Ŀ  |

|              |       | _    |      |       |             |      |                          |        | 1    | _                | _         |        | 1      | 1      |       |        |       |    |

|              | arc o |      | 6000 |       |             |      | _                        | out    | _    | _                | _         | 50.    | _      | _      | 00    | bo     |       | -  |

19

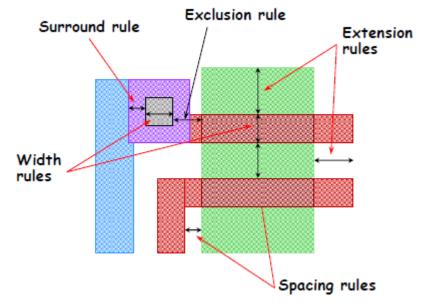

**Design Rules**

Intra-layer

- Widths, spacing, area

- Inter-layer

- Enclosures, distances, extensions, overlaps

- □ Special rules (sub-0.25µm)

- Antenna rules, density rules, (area)

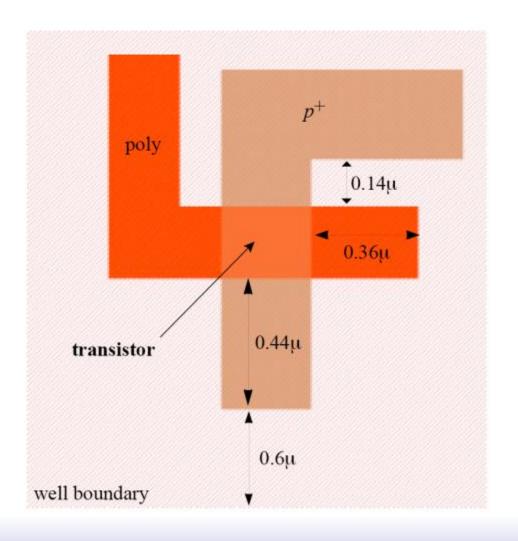

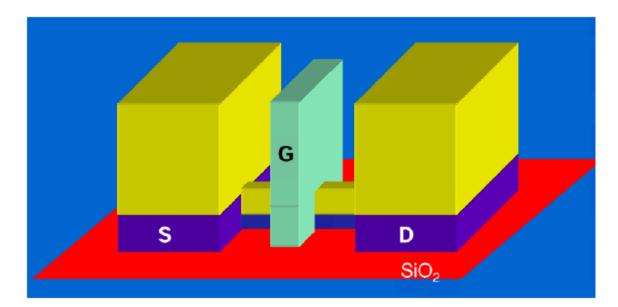

## **Transistor Layout**

22

## Why Have Design Rules?

- To be able to tolerate some level of fabrication errors such as

- 1. Mask misalignment

- 2. Dust

- 3. Process parameters (e.g., lateral diffusion)

4. Rough surfaces

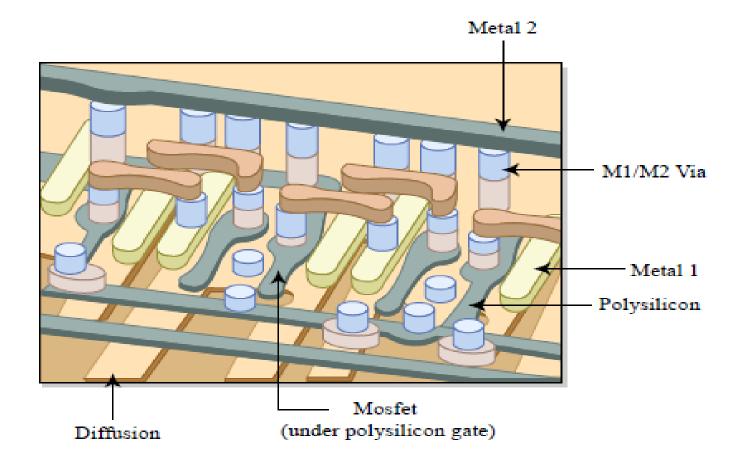

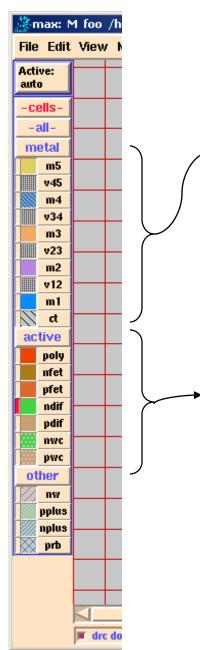

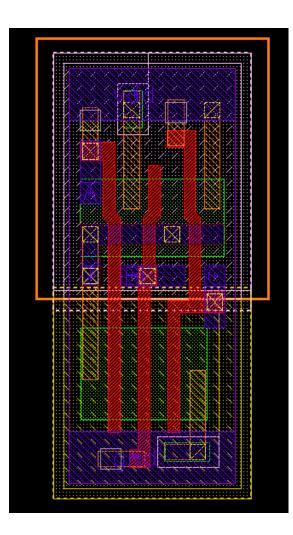

#### max Layer Representation

- Metals (five) and vias/contacts between the interconnect levels

- Note that m5 connects only to m4, m4 only to m3, etc., and m1 only to poly, ndif, and pdif

- Some technologies support "stacked vias"

- Active active areas on/in substrate (poly gates, transistor channels (nfet, pfet), source and drain diffusions (ndif, pdif), and well contacts (nwc, pwc))

- Wells (nw) and other select areas (pplus, nplus, prb)

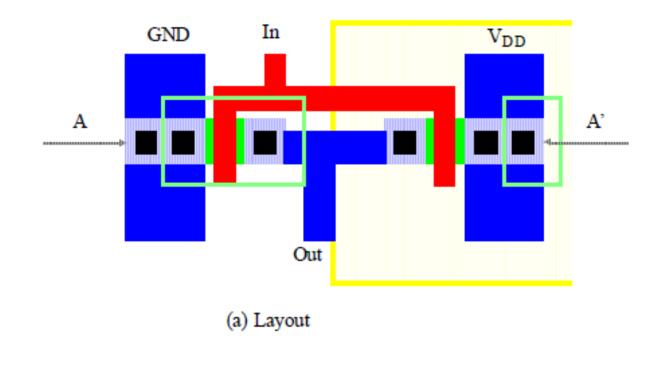

## CMOS Inverter max Layout

## Intra-Layer Design Rule Origins

- Minimum dimensions (e.g., widths) of objects on each layer to maintain that object after fab

- minimum line width is set by the resolution of the patterning process (photolithography)

- Minimum spaces between objects (that are *not* related) on the same layer to ensure they will not short after fab

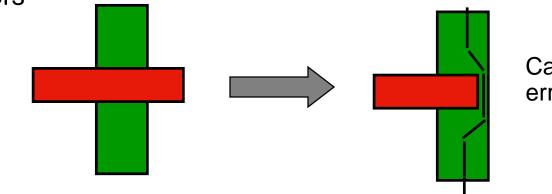

## Inter-Layer Design Rule Origins

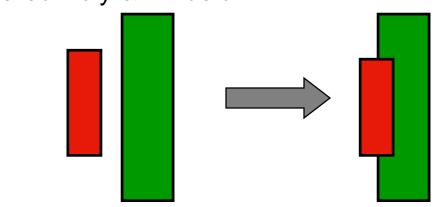

1. Transistor rules – transistor formed by overlap of active and poly layers

Transistors

Catastrophic error

**Unrelated Poly & Diffusion**

Thinner diffusion, but still working

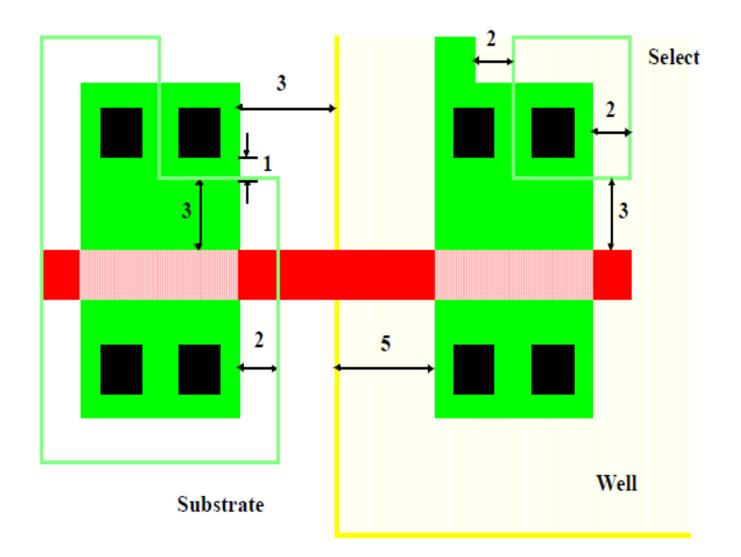

#### Inter-Layer: Well and Substrate

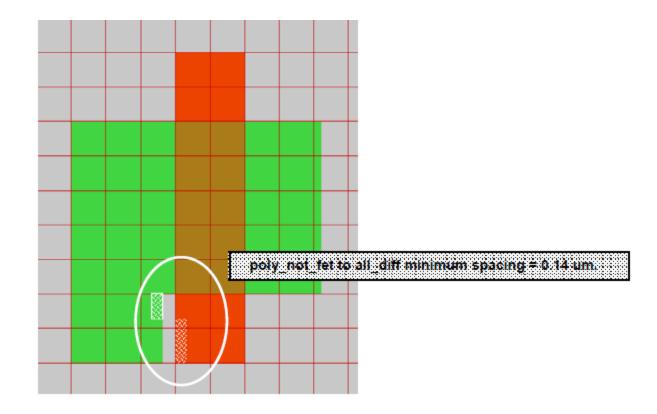

## Design Rule Checker

#### **Circuit Under Design**

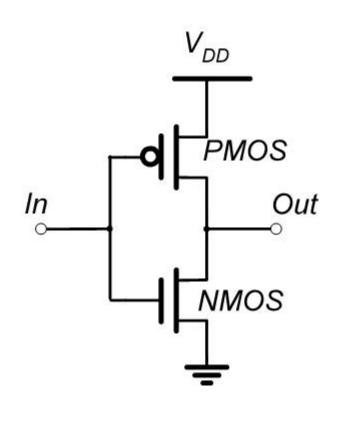

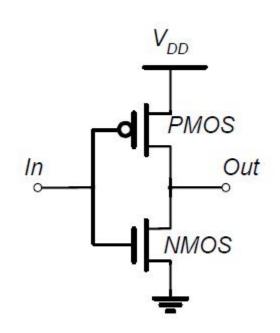

#### **CMOS Inverter**

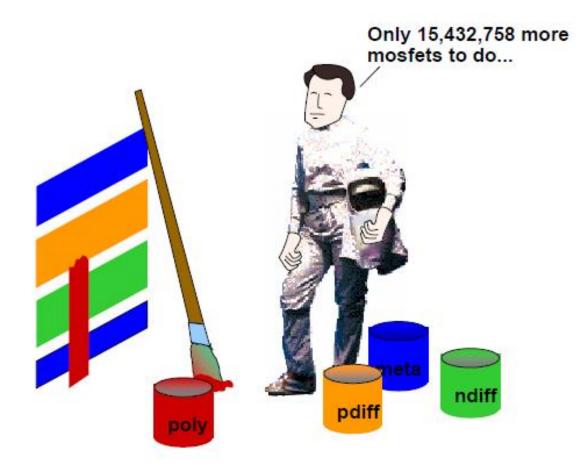

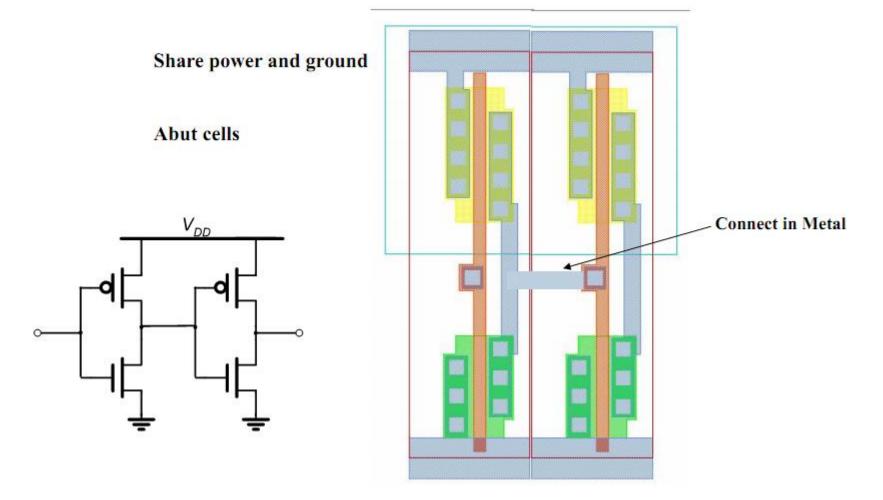

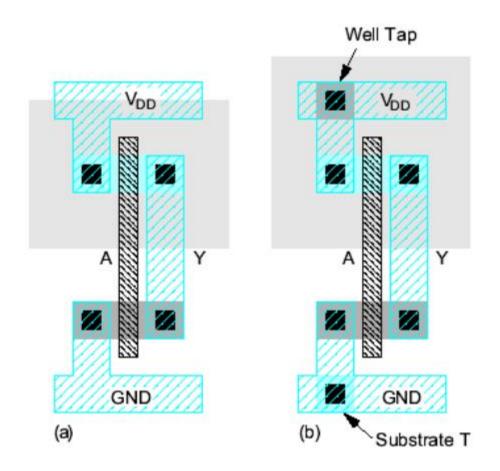

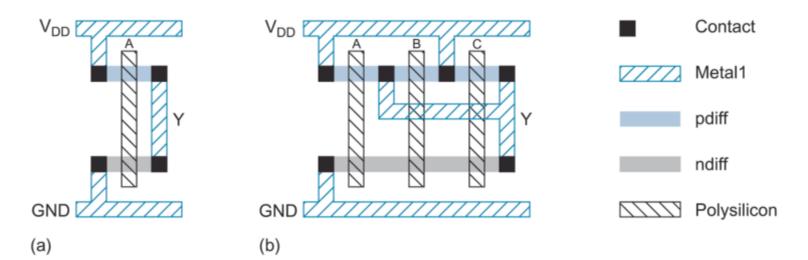

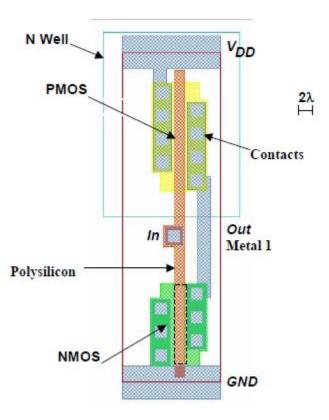

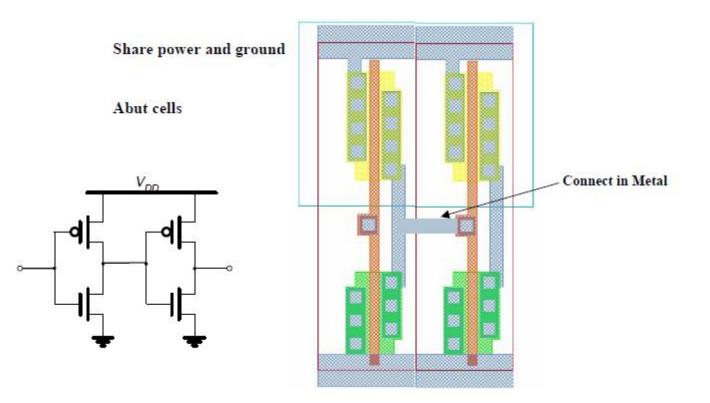

#### Gate Layout

Layout can be very time consuming

- Design gates to fit together nicely

- Build a library of standard cells

- Standard cell design methodology

- V<sub>DD</sub> and GND should abut (standard height)

- Adjacent gates should satisfy design rules

- nMOS at bottom and pMOS at top

- All gates include well and substrate contacts

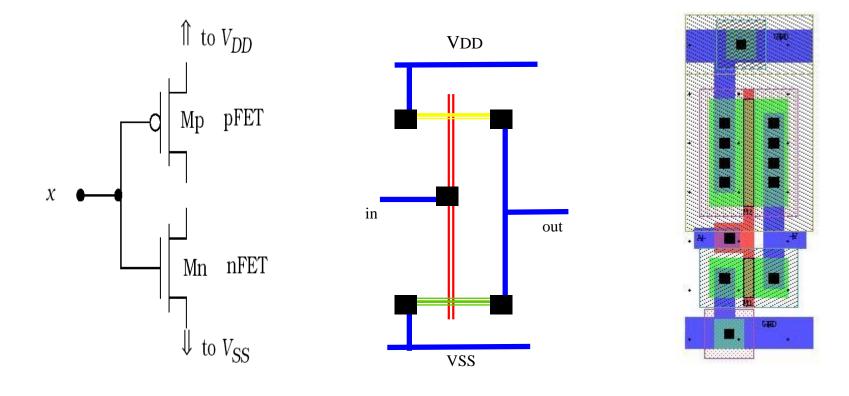

## Example: Inverter

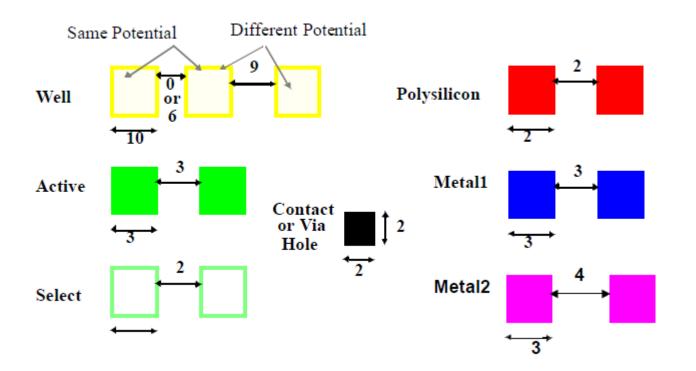

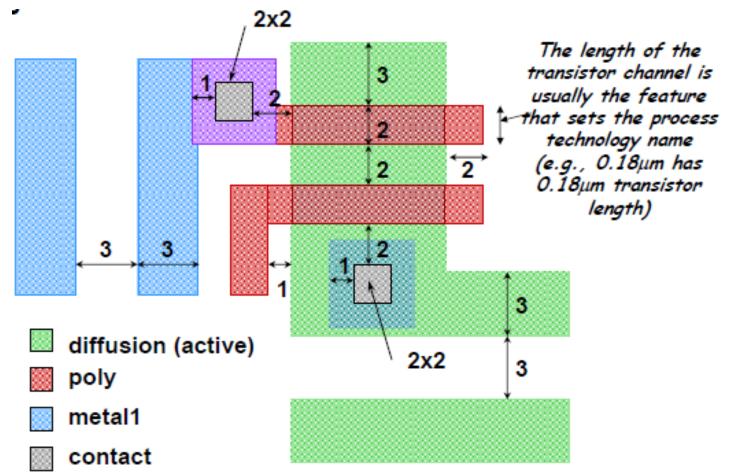

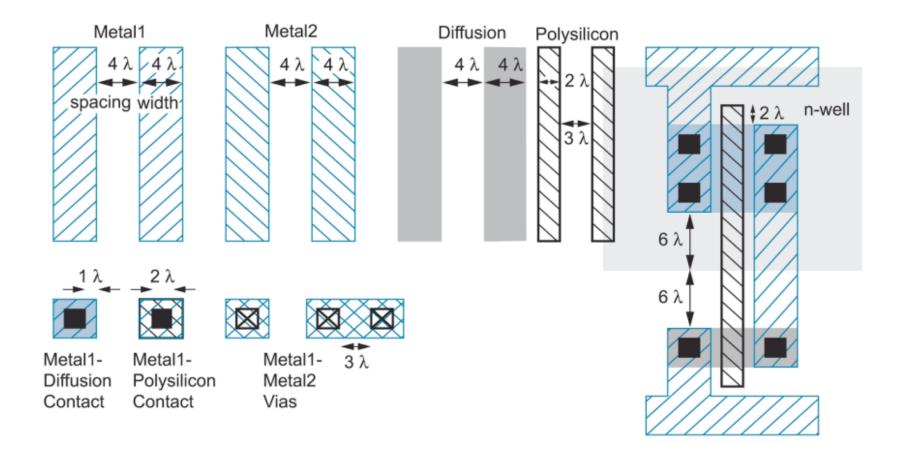

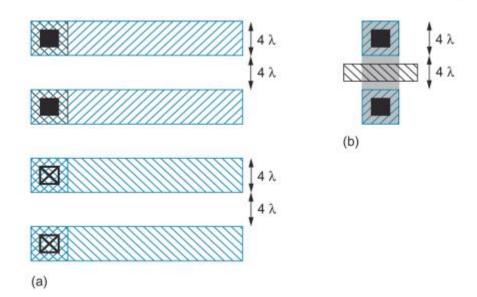

## Layout Design Rules Conservative rules to get started !

# **Design Rules Summary**

- Metal and diffusion have minimum width and spacing of 4λ

- Contacts are 2λ x 2λ and must be surrounded by 1λ on the layers above and below

- Polysilicon uses a width of 2λ

- Polysilicon overlaps diffusions by 2λ where a transistor is desired and has spacing or 1λ away where no transistor is desired

- Polysilicon and contacts have a spacing of 3λ from other polysilicon or contacts

- N-well surrounds pMOS transistors by 6λ and avoid nMOS transistors by 6λ

# The power and ground lines are called supply rails

$V_{DD}$

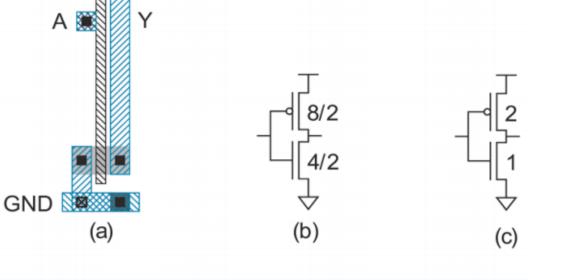

## **Inverter Layout**

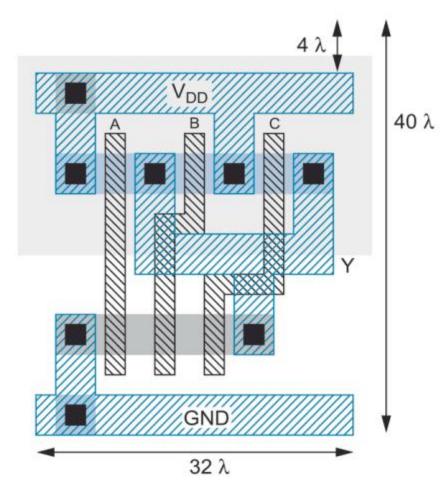

- Transistor dimensions specified as W / L ratio

- Minimum size is 4λ / 2λ, sometimes called 1 unit

**FIG 1.40** Inverter with dimensions labeled

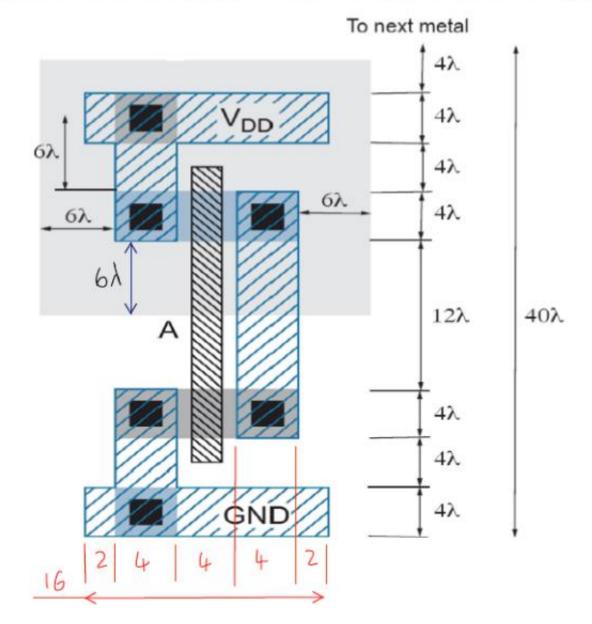

#### Inverter Standard Cell Area (1/2

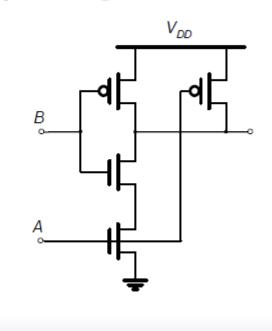

2-input NAND gate

#### **3-input Standard Cell NAND**

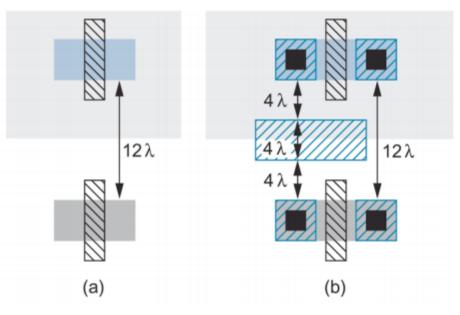

### Wiring Tracks

- A wiring track is the space required for a wire

- 4λ width, 4λ spacing from neighbor = 8λ pitch

- Transistors also consume one wiring track

#### Well Spacing

- Wells must surround transistors by 6λ

- Implies 12λ between opposite transistor flavors

- Leaves room for one wire track

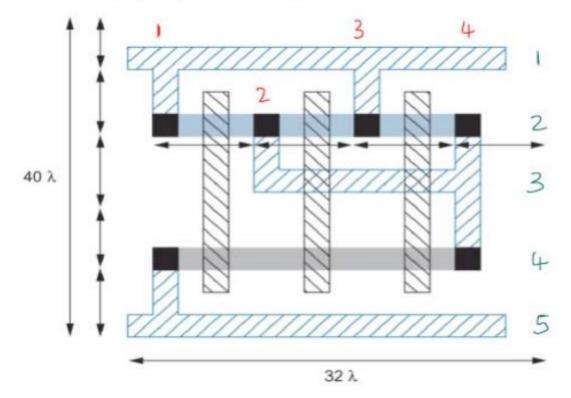

#### **Area Estimation**

- Estimate area by counting wiring tracks

- Multiply by 8 to express in λ

Horizontal 4×8 = 32 Vertical 5×8 = 40

#### **Stick Diagrams**

- Stick diagrams help plan layout quickly

- Need not be to scale

- Draw with color pencils or dry-erase markers

#### **CMOS Inverter Stick Diagrams**

• CMOS inverter described in other way.

### **Sticks Diagram**

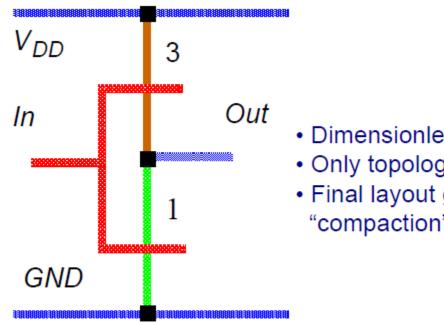

Stick diagram of inverter

- Dimensionless layout entities

- Only topology is important

- · Final layout generated by "compaction" program

#### **CMOS** Inverter

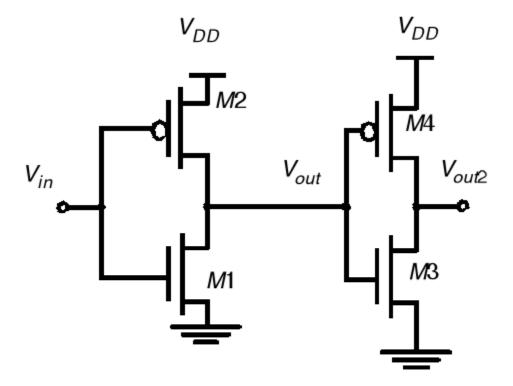

#### **Two Inverters**

#### Stick Diagram

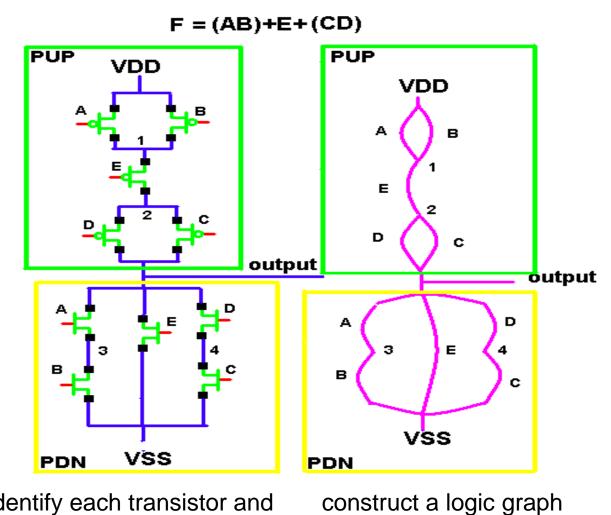

Identify each transistor and connection to the transistor by a unique name F = (AB)+E+(CD)

See the tutorial for further details.

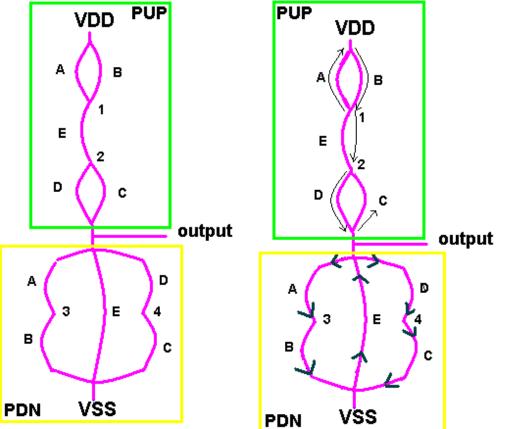

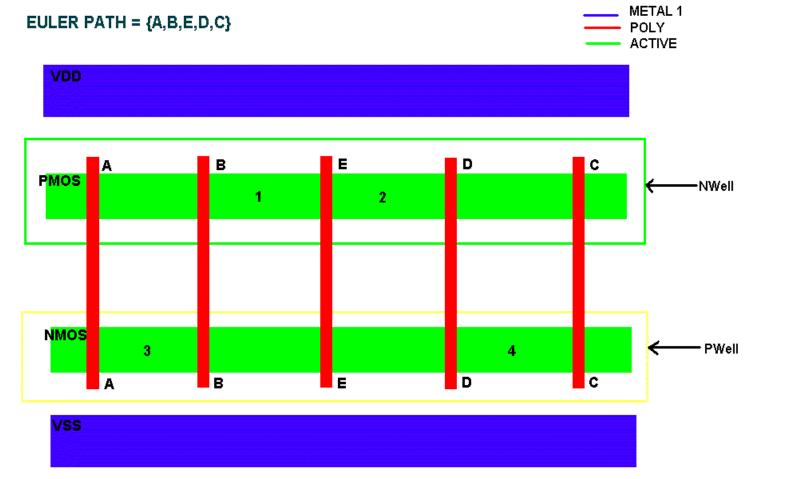

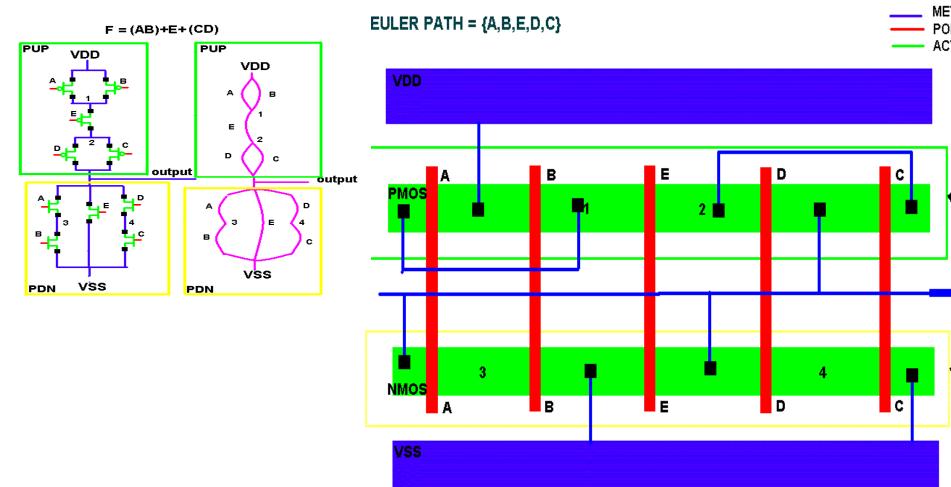

EULER PATH = {A,B,E,D,C}

- construct one Euler path for both the Pull up and Pull down network

-Trace two green lines horizontally to represent the NMOS and PMOS devices and surround them by n and p-wells

-Trace the number of inputs (5 in this example) vertically across each green strip and label them in order.

-Trace blue lines to represent VDD and VSS

-Place the connection labels upon the NMOS and PMOS devices

-Place the VDD, VSS and all output names upon the NMOS and PMOS devices -interconnect the devices based on Euler path.

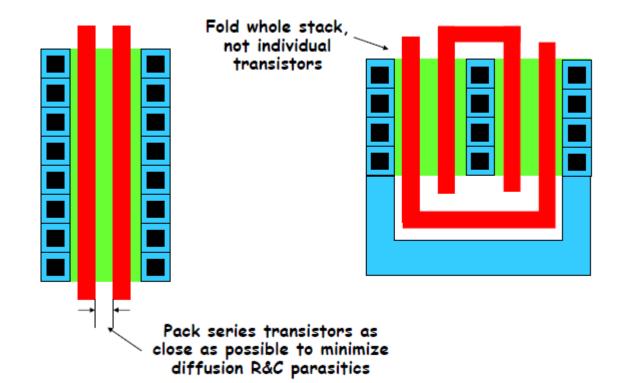

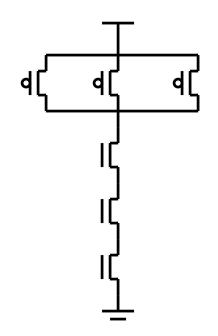

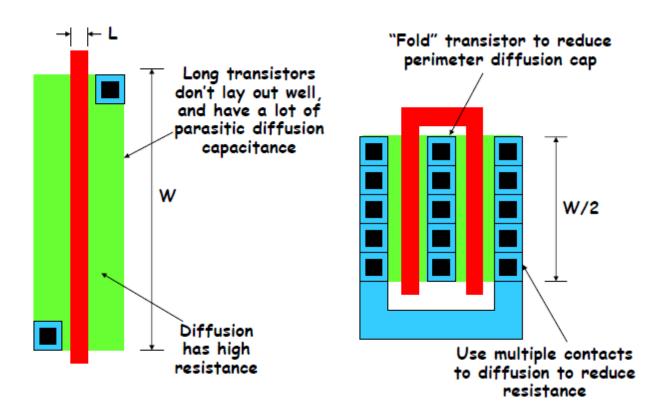

#### One finger

#### Two fingers (folded)

#### Less diffusion capacitance

#### Future device

25 nm MOS transistor (Folded Channel)

#### Layout vs. Schematic

### **Gate Layout Tricks**

### **Gate Layout Tricks**